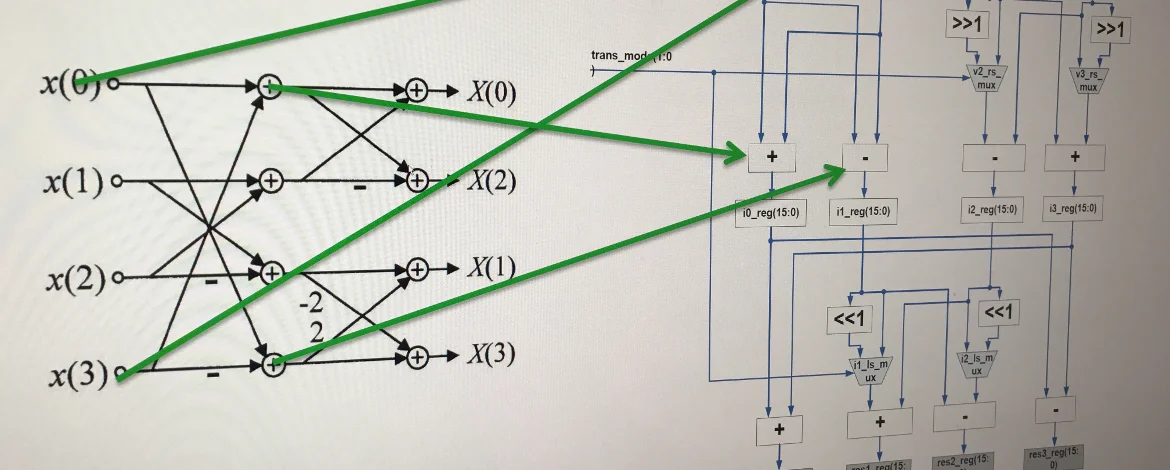

Die Professur „Architekturen eingebetteter Systeme für die Signalverarbeitung“ ist eine gemeinsame Berufung der Universität Potsdam und dem Fraunhofer-Institut für Nachrichtentechnik, Heinrich-Hertz- Institut in Berlin und widmet sich der Forschung in den drei wesentlichen Bereichen der Technischen Informatik Bild- und Videosignalverarbeitung, Hardwarearchitekturen und HW/SW Co-Design Methoden.

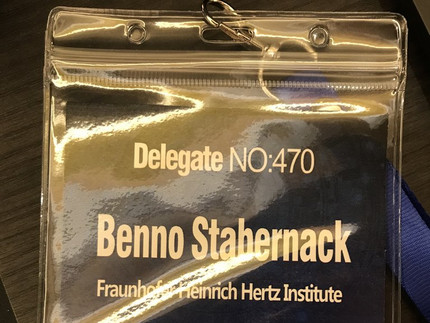

Der Lehrstuhl wird geleitet von Prof. Dr.-Ing. Benno Stabernack.

Neuigkeiten

Präsentation auf der ARCS 2026 zu unserem Open Source Framework für NAAs

Auf der diesjährigen ARCS 2026 (https://arcs-conference.org/home) in Mainz hat Niklas Schelten unser Paper mit dem Titel “A Flexible Open-Source Framework for FPGA-based Network-Attached Accelerators using SpinalHDL” präsentieren können.

B.S.

31.3.2026

Paper für den 33. Reconfigurable Architectures Workshop (RAW) angenommen

Unser Paper mit dem Titel „Using FPGA-based Network-Attached Accelerators for Energy-Efficient AI Training in HPC Datacenters“ wurde zur Präsentation auf dem 33. Reconfigurable Architectures Workshop (RAW) angenommen, der in Verbindung mit der IPDPS stattfindet.

Das Paper entstand in Zusammenarbeit mit unseren Projektpartnern ZIB, Universität Potsdam, GFZ und Perfacct (Steffen Christgau, Marco De Lucia, Max Lübke, Niklas Schelten, Bettina Schnor, Hannes Signer, Johannes Spazier, Benno Stabernack, Fritjof Steinert und Serhii Yahdzhyiev).

Die Arbeit ist Teil des Verbundprojekts NAAICE, das vom **BMBF** gefördert wird.

40th IEEE International Parallel & Distributed Processing Symposium : www.ipdps.org

40th IEEE International Parallel &

Distributed Processing Symposium

May 25-29, 2026

Marriott on Canal Street

New Orleans, USA

33rd Reconfigurable Architectures Workshop : raw.necst.it

BMBF Project NAAICE : www.greenhpc.eu

B.S. 6.3.2026

Herzlichen Glückwunsch zum Best Paper Award auf der PCS2025 !

Viktor Herrmann wurde vergangene Woche beim diesjährigen Picture Coding Symposium (PCS 2025) in Aachen ausgezeichnet.

Das Paper „UNNIP: Memory Optimized Universal Neural Network Intra-Prediction for Custom On-Chip Hardware-Architectures“ erreichte den 2. Platz bei der Verleihung des Best Paper Awards.

B.S. 19.12.2025

Herzlichen Glückwunsch, Herr Doktor Steinert !

Unser Mitarbeiter Fritjof Steinert hatte am 3.9. 2025 am Institut für Informatik die Disputation zu seiner Doktorarbeit mit dem Thema

„FPGA-based Network attached Accelerators: An Approach towards Energy-Efficient Computing in Data Centers“.

Herzlichen Glückwunsch !

B.S. 8.9.2025

Paper für den 34th Heterogeneity in Computing Workshop (HCW)auf der IPDPS Konferenz wurde angenommen

Unser Paper mit dem Titel "On the Usability and Energy Efficiency of High-Level Synthesis for FPGA-based Network-Attached Accelerators" wurde für die Präsentation auf dem 34th Heterogeneity in Computing Workshop (HCW) angenommen.

Das Paper wurde in Zusammenarbeit mit unseren Projektpartnern ZIB, Uni Potsdam, GfZ und Perfacct erstellt (Steffen Christgau, Dylan Everingham, Marco De Lucia, Max Lübke, Danny Puhan, Niklas Schelten, Bettina Schnor, Hannes Signer, Johannes Spazier, Benno Stabernack, Fritjof Steinert and Serhii Yahdzhyiev) und beschreibt unser neuesten Erkenntnisse hinsichtlich des produktiven Einsatzes unserer FPGA-basierten NAA Beschleuniger Architektur .

Das Paper enstand im Rahmen der Aktivitäten des BMBF geförderten Projektes NAAICE

39th IEEE International Parallel & Distributed Processing Symposium : www.ipdps.org

HCW 2025 - The thirty-fourth Heterogeneity in Computing Workshop : hcw-ipdps.org

BMBF Projekt NAAICE : www.greenhpc.eu

B.S. 23.03.2025

Neue Lehrveranstaltungen !

Wir starten auch in das kommende Wintersemester wieder mit neuen Lehrveranstaltungen aus dem Bereich der technischen Informatik.

Besonders hervorzuheben sind die Veranstaltungen ACA (Advanced Computer Architecture) und Computer Vision Hardware Architekturen

B.S. 26.9.2024

Semester erfolgreich abgeschlossen

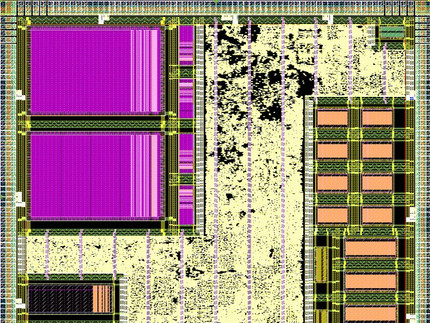

Zu den Highlights der Lehrveranstaltungen unseres Lehrstuhls gehört im Sommersemester die Veranstaltung System on Chip Architektuen, in der die Studierenden einen Einblick in den Entwurf hochperformanter Chip- und FPGA-Designs bekommen.

Im diesjährigen Praktikum zu dieser Veranstaltung lag der Fokus auf der echtzeitfähigen Videosignalverarbeitung, wobei eine Verarbeitungspipeline implementiert werden musste, die einen Kantendetektor auf Basis des Sobelfilter umsetzt.

19.7.24

Virtual FPGA Lab erfolgreich getestet

Um den Studierenden unserer Kurse die Möglichkeit zu geben mit unserer Laborausstattung auch unabhägig von den Lehrveranstaltungen zu experimentieren, haben wir ein sog. Virtual Lab für FPGAs prototypisch installiert.

Die Hardware kann damit remote genutzt werden, wobei eine Interaktion und die Kontrolle über die Hardware u.a. Internetkameras unter Einsatz einer CI Pipeline ermöglicht wird.

Das System wurde u.a. von den Studenten der SoCA (System on Chip Architekturen) Lehrveranstaltung gestestet und erfolgreich eingesetzt.

19.7.24

ARCS2024 in Potsdam

Der Lehrstuhl richtet die diesjährige ARCS Konferenz vom 14.5.-16.5. aus und wir freuen uns auf spannende Beiträge rund um das Thema "HPC - Challenges for Sustainable Computing".

Mehr Infos:

13.5.2024

BBKI Poster auf der HiPEAC2024

die Veranstalter der Konferenz HiPEAC2024 haben uns noch spontan die Möglichkeit gegeben, ein Poster zu präsentieren.

Diese Gelegenheit haben wir natürlich genutzt, um mit den Kollegen von den TUM unser BMBF Projekt BBKI zu präsentieren.

Mehr Infos zum Projekt finden sich hier :

www.uni-potsdam.de/de/multimedia/projekte/anwendungen/bb-ki-chips

20.1.2024

Präsentation Workshop Paper auf der HiPEAC 2024

Philipp Kreowsky hat unser Paper mit dem Titel “An Approach Towards Distributed DNN Training on FPGA Clusters” auf dem AccML Workshop im Rahmen der HiPEAC Konferenz vorstellen können.

Das Paper ist unter folgenden Links frei zugänglich: https://accml.dcs.gla.ac.uk/papers/2024/6th_AccML_paper_5.pdf

19.1.2024

Frohes Neues Jahr 2024 !

Die Mitarbeiter des Lehrstuhls wünschen ein frohes und vor allem erfolgreiches neues Jahr 2024 !

Wir starten dabei gleich mit zwei sehr erfreulichen Nachrichten:

AccML Workshop

Unsere Mitarbeiter Philipp Kreowsky und Justin Knapheide werden auf diesjährigen HiPEAC Konferenz 2024 in München am 17.1.2024 unser FPGA- basiertes Deep Learning Framework NADA im Rahmen des Accelerated Machine Learning Workshops AccML vorstellen.

https://www.hipeac.net/2024/munich/#/

https://accml.dcs.gla.ac.uk/

ARCS2024 Konferenz in Potsdam !

Weiterhin dürfen wir ankündigen, dass der Lehrstuhl die diesjährige ARCS2024 Konferenz vom 14.5.-16.5.2024 an der Uni Potsdam ausrichten wird, worüber wir uns sehr freuen.

3.1.2024

Herzlich willkommen!

Wir heißen unseren neuen Mitarbeiter Viktor Herrman in unserer Arbeitsgruppe herzlich willkommen.

Er wird in unserem Lab am Fraunhofer Heinrich Hertz Institut im Bereich effizienter Hardware Architekturen für neuartige Algorithmen der Videodatenkompression forschen.

2. November 2023

Semesterstart / Neue Veranstaltungen

Wir starten in das Wintersemester 2023/24 mit zwei weiteren neuen hochaktuellen Seminarveranstaltungen zu den Themen

Computer Vision Hardware Architekturen

Einschreibung wie immer über Puls.

Das AESS Team wünscht allen Studierenden einen guten Start ins WS2023/24 !

16.10.2023

Paper für Super Computing SC23 Workshop H2RC wurde angenommen

Unser Paper mit dem Titel “Enabling Communication with FPGA-based Network-attached Accelerators for HPC Workloads” wurde für den Workshop “H2RC” auf der Super Computing Conference SC23 angenommen.

Das Paper ist in Zusammenarbeit mit der Universität Potsdam (Bettina Schnor, Max Schroetter, Florian Mikolajczak), dem Zuse Institut Berlin (Steffen Christgau, Dylan Everingham) und dem Heinrich Hertz Institut Berlin / Uni Potsdam (Niklas Schelten, Benno Stabernack) entstanden und beschreibt die ersten Ansätze unsere FPGA-basierte NAA Beschleunigerarchitektur in das HPC Umfeld zu integrieren. Die Arbeiten sind Teil des vom Bmbf geförderten Verbundprojektes NAAICE

SC23 Conference : https://sc23.supercomputing.org/

H2RC Workshop: https://h2rc.cse.sc.edu/

BMBF Projekt NAAICE : https://www.greenhpc.eu/

20.9.2023

Herzlichen Glückwunsch !!

Zwei Doktoranden unseres Lehrstuhls, Philipp Kreowsky und Justin Knapheide, hatten die Gelegenheit auf der diesjährigen FPL 2023 (4 - 8 September 2023) in Göteborg, Schweden ihre Arbeiten vorzustellen.

Die Arbeiten befassen sich mit der Fragestellung, wie eine leistungsfähige, verlustleistungsarme Trainingsarchitektur für beliebige DCNN auf Basis von FPGA Clustern umgesetzt werden kann. Spezieller Fokus stellt dabei die Nutzung des am Lehrstuhl entwickelten NAA (Network Attached Accelerator) Konzepts dar.

Die gezeigten Poster können hier eingesehen werden:

Demonstrating NADA - A Workflow for Distributed CNN Training on FPGA Clusters

Challenges using FPGA Clusters for Distributed CNN Training

15.9.20232

Paper über die Nachhaltigkeitsanalyse unseres Network Attached Accelerator Konzepts wurde als Veröffentlichung angenommen.

Herzlichen Glückwunsch an Fritjof Steinert und die Co Autoren unseres Papers

"FPGA-based Network-attached Accelerators – An Environmental Life Cycle Perspective" für die ARCS2023!

Das Paper wurde angenommen und wird mit einem entsprechenden Vortrag auf der ARCS2023 Konferenz in Athen präsentiert.

Athen, Griechenland, 13-15. Juni, 2023

6. Juni 2023

Semesterstart mit neuer Veranstaltung

In diesem Sommersemester bieten wir zum ersten Mal die Veranstaltung System On Chip Architekturen an, die sich aus einer VL und einer Übung zusammensetzt. Wer also mehr über Rechnerarchitektur , Entwurf digitaler Schaltungen und Hardwarebeschreibungssprachen wissen möchte ist herzlich eingeladen.

Aufgrund der hohen Nachfrage, findet das Seminar Computer Graphics / Computer Vision in diesem Semester wiederum statt.

24.4.23

Radio Interview zum BMBF Projekt NAAICE

Im Rahmen der Radiosendung "Forschung aktuell - Computer und Kommunikation" des Deutschlandfunks konnte Benno Stabernack am 18.2.23 ein Interview geben und das im Projekt verwendete Grundkonzept des Network Attached Accelerators erläutern.

Die Sendung kann unter folgendem Link in der Mediathek des DLF gefunden werden:

23.2.23

Energieeffizentes Rechnen in HPC Rechenzentren unter Einsatz FPGA basierter NAAs - BMBF Projekt NAAICE gestartet.

Am 1.10.22 haben wir unser Verbundprojekt zum Thema enegieeffizientes Rechnen in HPC Rechenzentren (NAAICE) gestartet.

Das vom BMBF geförderte Projekt wird in unseren Labs am Fraunhofer Heinrich Hertz Institut durchgeführt.

Dabei werden von insgesamt fünf Partnern entsprechende Expertisen eingebracht, um die Integration von FPGAs in das HPC Umfeld einfach und anwenderfreundlich zu gestalten.

Weitere Informationen können u.a. hier gefunden werden:

SpinalHDL im Einsatz - Webinar am 16.12.2022

Philipp Kreowsky und Justin Knapheide aus unserer Arbeitsgruppe werden im Rahmen eines Online Webinars von ihren Erfahrungen beim Einsatz von SpinalHDL berichten. SpinalHDL ist eine spezielle Hardware Beschreibungssprache, die einen höheren Abstraktionsgrad als z.B. Verilog oder VHDL bietet aber im Gegensatz zu HighLevel Synthese Konzepten, die z.B. auf C basieren, eine hardwarenahe Beschreibung erlauben.

SpinalHDL wird z.Zt. bei uns zur Entwicklung unseres FPGA-basierten KI-Beschleunigerframeworks NADA eingesetzt.

Weitere Infos zum Webinar sind hier zu finden ->

https://user-images.githubusercontent.com/4832082/206420664-0c52a6e2-379f-4c3a-8876-8c2e68bc3375.jpg

Details zu SpinalHDL sind hier zu finden ->

spinalhdl.github.io/SpinalDoc-RTD/master/index.html

12.Dezember 2022

Video unseres FPGA-basierten ML-Beschleunigers ist online verfügbar

Das Demovideo unseres FPGA-basierten ML-Beschleunigers ist online:

In unserer Demonstration stellen wir eine neue Architektur netzwerkgekoppelter, energieeffizienter Beschleuniger für verteiltes maschinelles Lernen vor.

"Demonstration of a Distributed Accelerator Framework for Energy-efficient ML Processing"

vimeo.com/594479334

30. August 2021

IEEE OpenAccess Journal Paper veröffentlicht

Unsere Veöffentlichung mit dem Titel "A full-featured FPGA-based pipelined architecture for SIFT extraction" ist als OpenAcess Journal Paper verfügbar.

P. Kreowsky and B. Stabernack, "A full-featured FPGA-based pipelined architecture for SIFT extraction," in IEEE Access, doi: 10.1109/ACCESS.2021.3104387.

15. August 2021

Artikel über unser BMBF Forschungsprojekt Sysiko erschienen

Im Rahmen unseres BMBF geförderten Foschungsprojektes Sysiko (https://www.elektronikforschung.de/projekte/sysiko) entwicklen wir zuverlässige Methoden für die Erkennung von Gefahrensituationen mit Radfahrern im Staßenverkehr. Im Speziellen widmen wir uns der Vermeidung sog. Rechtsabbiegeunfälle mit LKWs und Bussen.

Eine Kurzdarstellung ist in der aktuellen Ausgabe des Uni Magazins Portal Wissen erschienen.

Portal Wissen

Das Forschungsmagazin der Universität Potsdam

Ausgabe Zwei 2021

Licht im toten Winkel, Seite 56ff.

www.uni-potsdam.de/de/up-entdecken/upaktuell/universitaetsmagazine

3. Juli 2021

Demonstration unseres FPGA-basierten ML-Beschleuniger auf der FPL2021 angenommen

Auf der diesjährigen FPL (31th International Conference on Field Programmable Logic and Applications) werden wir unseren FPGA-basierten ML Beschleuniger als Demosystem vorführen können.

Fritjof Steinert, Justin Knapheide and Benno Stabernack:

Demonstration of a Distributed Accelerator Framework for Energy Efficient ML Processing

31th International Conference on Field Programmable Logic and Applications

Virtual conference 31 August - 3 September 2021

cfaed.tu-dresden.de/fpl2021/welcome-to-fpl2021

8. Juni 2021

Neue Adresse

Das Institut für Informatik ist auf den Campus Golm umgezogen. Unser Lehrstuhl ist jetzt im neuen Gebäude an der Adresse zu finden:

An der Bahn 2

14476 Potsdam

Die Büros des Lehrstuhls befinden sich jetzt in der 1. Etage Ostflügel.

1.April 2021

Vortrag über unseren H.264/AVC Videoencoder mit ROI Feature auf dem nächsten DASIP 2021 Workshop

Unsere Veröffentlichung mit dem Titel "Architecture of a Low Latency H.264/AVC Video Codec for robust ML based Image Classification" verfasst von Benno Stabernack und Fritjof Steinert wurde angenommen und wird auf dem DASIP 2021 Workshop präsentiert.

18-20 Januar 2021, Budapest, Ungarn.

DASIP 2021: Workshop on Design and Architectures for Signal and Image Processing in conjunction with the 16th HiPEAC Conference

dasip2021.agh.edu.pl

2. Dezember 2020

Paper über unsere FPGA basierte RoCEv2 Remote DMA Protocol Engine wurde angenommen

Herzlichen Glückwunsch an Niklas Schelten und die Co Autoren unseres Papers

"A High-Throughput, Resource-Efficient Implementation of the RoCEv2 Remote DMA Protocol for Network-Attached Hardware Accelerators" für die FPT2020!

Das Paper wurde angenommen und wird mit einem entsprechenden Vortrag auf der viturellen Konferenz FPT2020 präsentiert.

Maui, Hawai, USA 7 to 11 December, 2020

International Conference on Field-Programmable Technology (FPT'20)

https://www.ece.ucf.edu/FPT2020

3. November 2020

Veröffentlichung über unser HW/SW Framework für FPGA-basiertes heterogenes Cloud Computing angenommen

Herzlichen Glückwunsch an Fritjof Steinert und die Co Autoren unseres Papers

"A Hardware/Software Framework for the Integration of FPGA-based Accelerators into Cloud Computing Infrastructures" für die IEEE SmartCloud 2020!

Das Paper wurde angenommen und wird mit einem entsprechenden Vortrag auf der viturellen Konferenz IEEE SmartCloud 2020 präsentiert.

November 6-8, Washington DC, USA

5th IEEE International Conference on Smart Cloud

www.cloud-conf.net/smartcloud/2020/

22. September 2020

Herzlich willkommen!

Wir heißen unseren neuen Mitarbeiter Justin Knapheide am Lehrstuhl "Architekturen eingebetteter Systeme für die Signalverarbeitung" herzlich willkommen.

Er wird im Bereich effizienter Hardware Architekturen für Anwendung des Maschinellen Lernens forschen.

15. Juli 2020

DSD2020 Veröffentlichung über unser Konzept für die Integration von netzwerkgekoppelten Hardwarebeschleunigern in Data Center angenommen

Herzlichen Glückwunsch an Fritjof Steinert und die Co Autoren unseres Papers

"Hardware and Software Components towards the Integration of Network-Attached Accelerators into Data Centers" für die DSD2020!

Das Paper wurde angenommen und wird mit einem entsprechenden Vortrag auf der Konferenz DSD2020 präsentiert.

August 26 – 28, 2020 Portorož | Slovenia

Euromicro Conference on Digital System Design

15.6.2020

FPL2020 Veröffentlichung zu Hardware Architekturen für FPGA basierte Neuronale Netze angenommen

Unsere Veröffentlichung mit dem Titel " A high throughput MobileNetV2 FPGA implementation based on a flexible architecture for depthwise separable convolution" , verfasst von Justin Knapheide, Benno Stabernack und Maximilian Kuhnke, wurde für die Präsentation auf der Konferenz FPL 2020 angenommen.

30th International Conference on Field Programmable Logic and Applications

Virtual conference 31 August - 4 September 2020

20.Mai 2020

Studentische Hilfskräfte gesucht!!

Für unser Labor am Fraunhofer HHI in Berlin suchen wir Studenten, die sich vornehmlich mit dem Hardwareentwurf befassen wollen. Im Speziellen suchen wir Interessierte, die uns beim Entwurf von Hochleistungshardware für KI-Algorithmen in Form von FPGA- oder ASIC-Umsetzung unterstützen wollen.

Mehr Informationen sind hier zu finden:

recruiting.fraunhofer.de/Vacancies/49128/Description/1

4. Dezember 2019

Benno Stabernack Mitglied des ARCS 2020 Program Committees

Prof. Benno Stabernack wurde eingeladen Mitglied des Program Committees der International Conference on Architecture of Computing Systems (ARCS 2020) zu sein, die vom 25-28. Mai 2020 in Aachen, Deutschland stattfindet.

15. November 2019

Herzlich willkommen!

Wir heißen unseren neuen Mitarbeiter Michał Steć am Lehrstuhl "Architekturen eingebetteter Systeme für die Signalverarbeitung" herzlich willkommen.

Er wird im Bereich Maschinelles Lernen und Video Signalverarbeitung forschen.

15. November 2019

Neues BMBF Forschungsprojekt gestartet

Am 1.8.2019 haben wir unser vom BMBF gefördertes Forschungsprojekt SySiKo am Lehrstuhl AESS gestartet.

Im Rahmen des Projektes werden wir Methoden und Verfahren entwickeln, die der Erhöhung der Verkehrssicherheit von Radfahrern und schwachen Verkehrsteilnehmern dienen soll. Zum Einsatz sollen dabei Verfahren des maschinellen Lernens kommen, die auf unterschiedliche Sensordaten angewandt werden.

In Zusammenarbeit mit unseren Verbundparntern werden wir ein FPGA basiertes System entwickeln, das im speziellen Verkehrsunfälle von Radfahrern mit LKW oder Bussen verhindern soll.

https://www.elektronikforschung.de/projekte/sysiko

22. September 2019

DASIP 2019, Paper über die Verarbeitung von Time of Flight Sensordaten wurde angenommen

Unser Paper mit dem Titel " Using Time-of-Flight Sensors for People Counting Applications" , verfasst von Michał Steć, Viktor Herrmann und Benno Stabernack, wurde für die Präsentation auf der Konferenz DASIP 2019 angenommen.

The Conference on Design and Architectures for Signal and Image Processing DASIP 2019

16 - 18 October, 2019, Montréal, Canada

19. July 2019

Paper über Sensordatenfusion für Fahrgastzählanwendungen angenommen

Unser Paper mit dem Titel " Multi-Sensor-Fusion System for People Counting

Applications" , verfasst von Michał Steć, Viktor Herrmann und Benno Stabernack, wurde für die Präsentation auf der Konferenz SAC 2019 angenommen.

Societal Automation Conference SA 2019

Technological & Architectural Frameworks

Krakow, 4-6 September 2019

12. Juli 2019

Benno Stabernack nimmt am MPEG125 / ITU VCEG/JCT-VC/JVET Meeting in Marrakesh , Marocco teil

Als Teil des ITU VCEG/JCT-VC/JVET Expert Teams hat Prof. Benno Stabernack die große Ehre am MPEG/ITU Meeting in Marrakesh, Marocco vom 9-18. Januar teilzunehmen, um an der Definition des nächsten Video Codierungs Standards VVC mitzuwirken. Er arbeitet hier u.a. an Fragen der Hardwarekomplexität.

9. Januar 2019

Demonstration des HNAA Cloud Computing Accelerators

Im Rahmen des M3D Abschlussworkshop konnte das von uns entwickelte Konzept zur Beschleunigung von rechenintensiven Workloads in der Cloud demonstriert werden.

Das HNAA (Heterogenous Network Attached Accelerator) genannte Konzept besteht dabei aus der Kombination von GPGPUs, FPGAs und Rechenkernen die über eine OpenStack Cloud Infrastruktur dem Anwender zur Verfügung stehen.

29. November 2018

Benno Stabernack Teilnehmer des ITU VCEG/JCT-VC/JVET Meetings in Macau SAR, China

Als Teil des ITU VCEG/JCT-VC/JVET Expert Teams nimmt Prof. Benno Stabernack am ITU Meeting in Macau SAR, China vom 3-12. Oktober teil, um an der Definition des nächsten Video Codierungs Standards VVC mitzuwirken.

2. Oktober 2018

ARCS2019 CfP

Der Call for Paper für die International Conference on Architecture of Computing Systems (ARCS 2019) wurde veröffentlicht.

arcs2019.itec.kit.edu/download/ARCS2019.pdf

22. Spetember 2018

Benno Stabernack Mitglied des ARCS 2019 Program Committees

Prof. Benno Stabernack wurde eingeladen Mitglied des Program Committees der International Conference on Architecture of Computing Systems (ARCS 2019) zu sein, die vom 20-23. Mai in Copenhagen, Dänemark stattfindet.

22. September 2018

Herzlich willkommen!

Wir heißen unseren neuen Mitarbeiter Tim Jacquemot herzlich willkommen am Lehrstuhl "Architekturen eingebetteter Systeme für die Signalverarbeitung". Er wird im Bereich algorithmischer Komplexität von Video Signalverarbeitungsverfahren forschen.

2. Mai 2018

Herzlichen Glückwunsch!

Unser ehemaliger Mitarbeiter Jens Brandenburg hat seine Dissertation mit dem Titel „Generische Analysemethoden für den Systementwurf heterogener eingebetteter Mehrkernsysteme“ an der Friedrich-Alexander-Universität (FAU) Erlangen-Nürnberg mit dem Gesamturteil magna cum laude abgeschlossen. Die Arbeit entstand in Zusammenarbeit der FAU Erlangen-Nürnberg (Lehrstuhls für Informatik 3 - Rechnerarchitektur) mit dem Fraunhofer Heinrich-Hertz-Institut HHI (Forschungsgruppe Eingebettete Systeme der Abteilung Videokodierung und Maschinelles Lernen).

Die Prüfungskommission unter dem Vorsitz von Prof. Dr.-Ing. Felix Freiling (FAU Erlangen-Nürnberg) bestand aus dem ersten Gutachter Prof. Dr.-Ing. Dietmar Fey (FAU Erlangen-Nürnberg), dem zweiter Gutachter Prof. Dr.-Ing. Benno Stabernack (Universität Potsdam/Fraunhofer HHI) und dem dritten Prüfer Prof. Dr.-Ing. André Kaup (FAU Erlangen-Nürnberg).

20. März 2018

Projektstart Forschungsprojekt „Next Generation Video Coding“

Am Lehrstuhl ist zum 1.12.2017 das Projekt „Next Generation Video Coding“ gestartet.

Mit der Effizienzsteigerung neuester Videocodierungsverfahren geht auch eine drastische Steigerung der Komplexität eingesetzter Algortihmen und damit auch der benötigten Rechenzeit einher. Das Projekt widmet sich der Analyse, der Optimierung und dem Entwurf von Verfahren zur Videocodierung in speziellem Hinblick auf aufwandseffiziente Hardwareumsetzungen.

In den nächsten Tagen wird hierzu eine Stellenanzeige für eine Doktorandenstelle im Rahmen des Projektes veröffentlicht.

1.12.2017

ARCS2020 CfP

Der Call for Paper für die International Conference on Architecture of Computing Systems (ARCS 2020) wurde veröffentlicht.

arcs2020.itec.kit.edu/download/ARCS2020.pdf

15. November 2019