The chair of „Embedded Systems Architectures for Signalprocessing“ has been established as a joint appointment of the University of Potsdam and the Fraunhofer Institute for Telecommunications, Heinrich Hertz Institute, Berlin / Germany. The research activities are focused on three main areas Image- and Videoprocessing, Hardware Architectures and HW/SW Co-Design Methodologies.

Chairholder is Prof. Dr.-Ing. Benno Stabernack.

News

Congratulations on the Best Paper Award at PCS 2025!

Viktor Herrmann was honored last week at this year’s Picture Coding Symposium (PCS 2025) in Aachen.

The paper “UNNIP: Memory Optimized Universal Neural Network Intra-Prediction for Custom On-Chip Hardware Architectures” received second place in the Best Paper Award competition.

More information is available here ->

B.S. 19.12.2025

Congratulations Dr. Steinert !

On September 3rd. 2025 our collegue Fritjof Steinert has successfully defended his doctoral thesis entitled

"FPGA-Based Network Attached Accelerator: to Approach Toward's Energy Efficient Computing in Data Centers"

at the Institute of Computer Science.

Congratulations !

B.S. 8.9.2025

Paper for the 34th Heterogeneity in Computing Workshop (HCW), held in conjunction with IPDPS has been accepted

Our paper entitled “On the Usability and Energy Efficiency of High-Level Synthesis for FPGA-based Network-Attached Accelerators” has been accepted for presentation at the workshop “34th Heterogeneity in Computing Workshop (HCW), held in conjunction with IPDPS.

The paper has been written in collaboration with our project partners ZIB, Uni Potsdam, GfZ and Perfacct (Steffen Christgau, Dylan Everingham, Marco De Lucia, Max Lübke, Danny Puhan, Niklas Schelten, Bettina Schnor, Hannes Signer, Johannes Spazier, Benno Stabernack, Fritjof Steinert and Serhii Yahdzhyiev) and describes the newest findings regarding usability aspects of our FPGA-based NAA accelerator architecture .

The work is part of the NAAICE joint project funded by the BMBF

39th IEEE International Parallel & Distributed Processing Symposium : www.ipdps.org

HCW 2025 - The thirty-fourth Heterogeneity in Computing Workshop : hcw-ipdps.org

BMBF Project NAAICE : www.greenhpc.eu

B.S. 23.03.2025

New Courses !

We are starting the coming winter semester with new courses in the field of technical computer science.

The events are particularly noteworthy ACA (Advanced Computer Architecture) und Computer Vision Hardware Architekturen

B.S. 26.9.2024

Semester successfully completed

One of the highlights in the summer semester is the System on Chip Architecture course, in which students gain an insight into the design of high-performance chip and FPGA designs.

In this year, the focus was on real-time capable video signal processing, whereby a processing pipeline had to be implemented that implements an edge detector based on the Sobel filter.

19.7.24

Virtual FPGA Lab tested successfully

In order to give the students of our courses the opportunity to experiment with our laboratory equipment independently of the courses, we have installed a so-called virtual lab for FPGAs as a prototype.

The hardware can therefore be used remotely, enabling interaction and control over the hardware, including internet cameras by using a CI pipeline .

The system was tested and used successfully by the students of the SoCA (System on Chip Architectures) course, among others.

19.7.24

ARCS2024 in Potsdam

The chair is organizing this year's ARCS conference from May 14th to May 16th. and we look forward to exciting contributions on the topic "HPC - Challenges for Sustainable Computing".

The event will take place at our lovely Campus Griebnitzsee.

More infos can be found here:

13.5.2024

BBKI Poster at the HiPEAC2024

The organizers of the HiPEAC2024 conference spontaneously gave us the opportunity to present a poster.

Of course, we took this opportunity to present our BMBF project BBKI with our colleagues from TUM.

More information about the project can be found here:

www.uni-potsdam.de/de/multimedia/projekte/anwendungen/bb-ki-chips

20.1.2024

Workshop paper presentation at HiPEAC 2024

Philipp Kreowsky presented our paper with the title “An Approach Towards Distributed DNN Training on FPGA Clusters” at AccML Workshop as part of the HiPEAC conference.

The paper is freely accessible under the following links: https://accml.dcs.gla.ac.uk/papers/2024/6th_AccML_paper_5.pdf

19.1.2024

Happy New Year 2024!

The staff of the chair wishes you a happy and, above all, successful New Year 2024 !

We're starting with two very good news:

AccML Workshop

Our researcher Philipp Kreowsky and Justin Knapheide will present our FPGA-based deep learning framework NADA at this year's HiPEAC Conference 2024 in Munich on January 17th, 2024 as part of the Accelerated Machine Learning Workshop AccML.

www.hipeac.net/2024/munich/

accml.dcs.gla.ac.uk

ARCS2024 Conference in Potsdam!

We can also announce that the chair will host this year's ARCS2024 conference from May 14th to May 16th, 2024 at the University of Potsdam, which we are very happy about.

3.1.2024

Welcome !

We welcome our new group member Viktor Herrmann.

He will work in our Labs at the Fraunhofer Heinrich Hertz Institute as a researcher in the field of advanced hardware architectures for new algorithms for video data compression.

2. November 2023

Start of Semester / New courses

We are starting the winter semester 2023/24 with two more new, highly up-to-date seminar courses on these topics:

Computer Vision Hardware Architekturen

As always, please register via Puls.

The AESS team wishes all students a good start to the WS2023/24!

16.10.2023

Paper for the Super Computing SC23 Workshop H2RC has been accepted

Our paper entitled “Enabling Communication with FPGA-based Network-attached Accelerators for HPC Workloads” has been accepted for presentation at the workshop “H2RC” of the Super Computing Conference SC23.

The paper has been written in collaboration with the University of Potsdam (Bettina Schnor, Max Schroetter, Florian Mikolajczak), the Zuse Institute Berlin (Steffen Christgau, Dylan Everingham) and the Heinrich Hertz Institute Berlin / University of Potsdam (Niklas Schelten, Benno Stabernack) and describes the first approaches of integrating our FPGA-based NAA accelerator architecture into the HPC environment.

The work is part of the NAAICE joint project funded by the BMBF

SC23 Conference : https://sc23.supercomputing.org/

H2RC Workshop: https://h2rc.cse.sc.edu/

BMBF Projekt NAAICE : https://www.greenhpc.eu/

20.9.2023

Congratulations !!

Two of our Phd. students, Philipp Kreowsky and Justin Knapheide, had the opportunity to present their work at this year's FPL 2023 (September 4 - 8, 2023) in Gothenburg, Sweden.

The work addresses the question of how a powerful, low-power training architecture for a wide range of DCNNs based on FPGA clusters can be implemented.

A special focus is on the use of the NAA (Network Attached Accelerator) concept developed at the chair.

The presented posters can be found here :

Demonstrating NADA - A Workflow for Distributed CNN Training on FPGA Clusters

Challenges using FPGA Clusters for Distributed CNN Training

15.9.20232

Paper about a sustainablity analysis of our Network Attached Accelerator concept has been accepted for publication.

Congratulation to Fritjof Steinert and the co-authors of our paper entitled

"FPGA-based Network-attached Accelerators – An Environmental Life Cycle Perspective" at the ARCS 2023 conference !

The paper has been accepted and will be presented with a corresponding talk in Athens.

Athens, Greece, 13-15. June, 2023

6. June 2023

New courses

This summer semester we are offering the course System On Chip Architekturen for the first time, which consists of a lecture and an exercise. Anyone who would like to know more about computer architecture, the design of digital circuits and the usage of hardware description languages is cordially invited.

Due to the high demand, the Computer Graphics / Computer Vision seminar will take place again this semester.

24.4.23

Radio interview about the BMBF project NAAICE

Benno Stabernack was able to give an interview on February 18th, 2023 as part of the Deutschlandfunk radio program "Research current - computer and communication" and explain the basic concept of the Network Attached Accelerator used in the project.

The program can be found under the following link in the DLF media library:

23.2.23

Energy-efficient computing in HPC data centers using FPGA-based NAAs - BMBF project NAAICE started.

On October 1st, 2022 we started our joint project on energy-efficient computing in HPC data centers (NAAICE).

The project funded by the BMBF is carried out in our labs at the Fraunhofer Heinrich Hertz Institute.

A total of five partners bring in relevant expertise to make the integration of FPGAs into the HPC environment simple and user-friendly.

Further information can be found here:

December 17th 2022

Using SpinalHDL - Webinar December 16. 2022

Philipp Kreowsky and Justin Knapheide of our work group will report in an online webinar on their experiences using SpinalHDL.

SpinalHDL is a special hardware description language that offers a higher degree of abstraction than e.g. Verilog or VHDL, but in contrast to high-level synthesis concepts that are e.g. based on C, allow a hardware-related description.

SpinalHDL is currently used by us to develop our FPGA-based AI accelerator framework NADA.

More information about the webinar can be found here ->

https://user-images.githubusercontent.com/4832082/206420664-0c52a6e2-379f-4c3a-8876-8c2e68bc3375.jpg

Further information regarding SpinalHDL can be found here ->

spinalhdl.github.io/SpinalDoc-RTD/master/index.html

December 12th , 2022

Video of our FPGA based ML accelerator online

The demo video of our FPGA-based ML accelerator is online.

In our demonstration, we introduce a new architecture of directly network-coupled accelerators for distributed machine learning to achieve higher energy efficiency.

"Demonstration of a Distributed Accelerator Framework for Energy-efficient ML Processing"

vimeo.com/594479334

August 30, 2021

IEEE OpenAccess Journal Paper published

Our paper entitled "A full-featured FPGA-based pipelined architecture for SIFT extraction" is as an OpenAcess Journal Paper available.

P. Kreowsky and B. Stabernack, "A full-featured FPGA-based pipelined architecture for SIFT extraction," in IEEE Access, doi: 10.1109/ACCESS.2021.3104387.

August 15, 2021

Article about our Bmbf research project Sysiko published

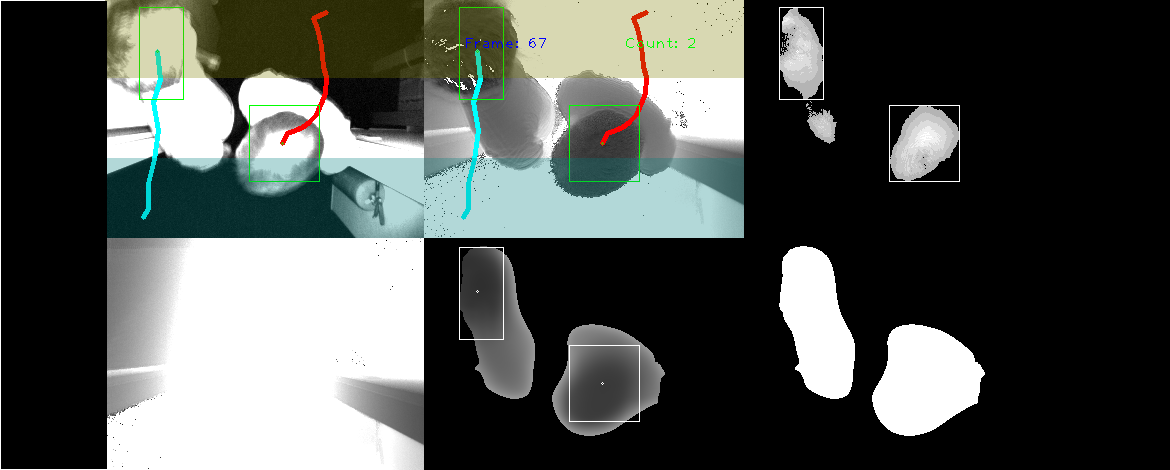

As part of our BMBF-funded research project Sysiko (https://www.elektronikforschung.de/projekte/sysiko) , we develop reliable methods for the detection of dangerous situations with cyclists in road traffic. In particular, we are dedicated to avoiding so-called right-turn accidents with trucks and buses.

A brief description was published in the current issue of the university magazine Portal Wissen.

Portal Wissen

Das Forschungsmagazin der Universität Potsdam

Ausgabe Zwei 2021

Licht im toten Winkel, Seite 56ff.

www.uni-potsdam.de/de/up-entdecken/upaktuell/universitaetsmagazine

July 3, 2021

Demonstration of our FPGA-based ML-accelerator for the FPL2021 accepted

We will demontrate our FPGA-based ML accelerator on this years FPL (31th International Conference on Field Programmable Logic and Applications).

Fritjof Steinert, Justin Knapheide and Benno Stabernack:

Demonstration of a Distributed Accelerator Framework for Energy Efficient ML Processing

31th International Conference on Field Programmable Logic and Applications

Virtual conference 31 August - 3 September 2021

cfaed.tu-dresden.de/fpl2021/welcome-to-fpl2021

June 8 2021

New Address

The Institute for Computer Science moved over to our new building located on the university campus in Potsdam Golm.

The new address is:

An der Bahn 2

14476 Potsdam

Our Offices are located in the first floor of the building.

April 1st, 2021

We will present our H.264/AVC Videoencoder with ROI Feature at the upcoming DASIP 2021 Workshop

Our paper entitled "Architecture of a Low Latency H.264/AVC Video Codec for robust ML based Image Classification" by Benno Stabernack and Fritjof Steinert has been accepted and will be presented with a corresponding lecture at the virtual workshop DASIP 2021 as part of the HiPEAC Conference.

18-20 January 2021, Budapest, Hungary.

DASIP 2021: Workshop on Design and Architectures for Signal and Image Processing in conjunction with the 16th HiPEAC Conference

dasip2021.agh.edu.pl

December 2 , 2020

Paper about our FPGA based RoCEv2 Remote DMA Protocol engine has been accepted for publication

Congratulations to Niklas Schelten and the co-authors of our paper entitled "A High-Throughput, Resource-Efficient Implementation of the RoCEv2 Remote DMA Protocol for Network-Attached Hardware Accelerators" at the FPT2020!

The paper has been accepted and will be presented with a corresponding lecture at the virtual conference.

Maui, Hawai, USA 7 to 11 December, 2020

International Conference on Field-Programmable Technology (FPT'20)

https://www.ece.ucf.edu/FPT2020

November 3 , 2020

Publication about our HW/SW Framework for FPGA enabled heterogenous Cloud Computing has been accepted

Congratulations to Fritjof Steinert and the co-authors of our paper entitled "A Hardware/Software Framework for the Integration of FPGA-based Accelerators into Cloud Computing Infrastructures" at the IEEE SmartCloud 2020!

The paper has been accepted and will be presented with a corresponding lecture at the virtual conference IEEE SmartCloud 2020.

November 6-8, Washington DC, USA

5th IEEE International Conference on Smart Cloud

www.cloud-conf.net/smartcloud/2020/

September 22nd , 2020

Welcome !

We welcome our new group member Justin Knapheide at the chair of "Embedded Systems Architectures for Signal Processing".

He will work as a researcher in the field of advanced hardware architectures for machine learning .

July 15, 2020

DSD2020 Publication about our concept for the integration of network-attached hardware accelerators in data centers accepted

Congratulations to Fritjof Steinert and the co-authors of our paper entitled "Hardware and Software Components towards the Integration of Network-Attached Accelerators into Data Centers" at the DSD2020!

The paper has been accepted and will be presented with a corresponding lecture at the conference DSD2020.

August 26 – 28, 2020 Portorož | Slovenia

Euromicro Conference on Digital System Design

June 15, 2020

FPL2020 Paper on Hardware Architectures for FPGA based Neural Nets accepted

Our Paper entitled " A high throughput MobileNetV2 FPGA implementation based on a flexible architecture for depthwise separable convolution" authored by Justin Knapheide, Benno Stabernack and Maximilian Kuhnke, has been accepted for presentation on the

30th International Conference on Field Programmable Logic and Applications

held as virtual conference 31 August - 4 September 2020

May 20, 2020

einstellung

Benno Stabernack member of ARCS 2020 program committee

Prof. Benno Stabernack, has been invited to join the program committee of the International Conference on Architecture of Computing Systems (ARCS 2020) to be held from May 25, 2020 through May 28, 2020 in Aachen, Germany.

http://arcs2020.itec.kit.edu/

November 15, 2019

ARCS2020 CfP

Call for Paper for the upcoming International Conference on Architecture of Computing Systems (ARCS 2020) has been published.

arcs2020.itec.kit.edu/download/ARCS2020.pdf

November 15, 2019

Welcome !

We welcome our new group member Michał Steć at the chair of "Embedded Systems Architectures for Signal Processing".

He will work in the field of machine learning and video signal processing.

November 15, 2019

New Research Project started

On 1st of August 2019 we started the BMBF funded project SySiKo on enhancing the traffic safety for bicycle drivers .

In the course of the project we will investigate and develop machine learning powered image recognition algorithms to detect critical situations in nowadays tight urban traffic. In cooperation with our partners a complete FPGA based system will be developed.

The goal is to drastically reduce the number of accidents of bicycle drivers with cars and especially with busses and trucks.

https://www.elektronikforschung.de/projekte/sysiko

September 22th, 2019

DASIP 2019 Paper on processing of Time of Flight sensor data accepted

Our Paper entitled " Using Time-of-Flight Sensors for People Counting Applications" authored by Michał Steć, Viktor Herrmann and Benno Stabernack, has been accepted for presentation on the

The Conference on Design and Architectures for Signal and Image Processing DASIP 2019

16 - 18 October, 2019, Montréal, Canada

July 19th, 2019

Paper on sensor data fusion for people counting application accepted

Our Paper entitled " Multi-Sensor-Fusion System for People Counting

Applications" authored by Michał Steć, Viktor Herrmann and Benno Stabernack, has been accepted for presentation on the first international

Societal Automation Conference SA 2019

Technological & Architectural Frameworks

Krakow, 4-6 September 2019

July 12th, 2019

Benno Stabernack participate MPEG125 / ITU VCEG/JCT-VC/JVET Meeting Marrakesh , Morocco

As part of ITU VCEG/JCT-VC/JVET expert team Prof. Benno Stabernack has the great honor to participate the MPEG/ITU meeting in Marrakesh, Morocco from January 9-18 to work on the next upcoming video coding standard VVC.

January 9nd, 2019

Public Demonstration of HNAA Cloud Computing Accelerator

As part of the M3D final workshop, we were able to demonstrate our concept for accelerating compute-intensive workloads in the cloud.

The HNAA (Heterogeneous Network Attached Accelerator) named concept consists of the combination of GPGPUs, FPGAs and computing cores, which are available to the user via a OpenStack cloud infrastructure.

November 29nd, 2018

ARCS2019 CfP

Call for Paper for the upcoming International Conference on Architecture of Computing Systems (ARCS 2019) has been published.

arcs2019.itec.kit.edu/download/ARCS2019.pdf

September 22nd, 2018

Benno Stabernack member of ARCS 2019 program committee

Prof. Benno Stabernack, has been invited to join the program committee of the International Conference on Architecture of Computing Systems (ARCS 2019) to be held from May 20, 2019 through May 23, 2019 in Copenhagen, Denmark.

September 22nd, 2018

Welcome !

We welcome our new group member Tim Jacquemot at the chair of "Embedded Systems Architectures for Signal Processing". He will work in the field of algorithmic complexity of video signal processing.

2nd May, 2018

Congratulations !

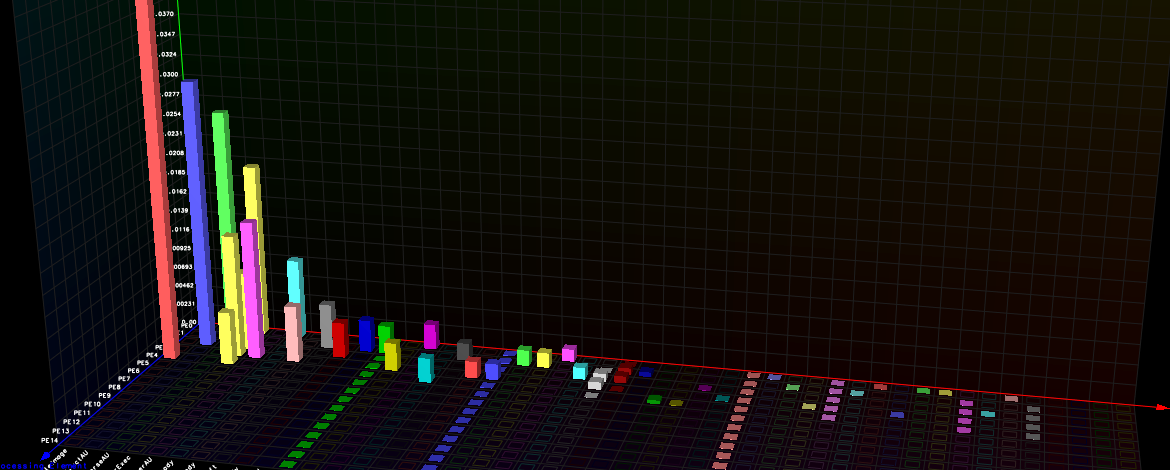

Our former Group Member Jens Brandenburg completed his dissertation entitled „Generische Analysemethoden für den Systementwurf heterogener eingebetteter Mehrkernsysteme“ ("Generic Analysis Methods for the Design of Heterogeneous Embedded Multi-Core Systems") at the Friedrich-Alexander-University (FAU) Erlangen-Nuremberg with magna cum laude.

The examination board chaired by Prof. Dr.-Ing. Felix Freiling (FAU Erlangen-Nuremberg) consisted of the first expert Prof. Dr.-Dietmar Fey (FAU Erlangen-Nuremberg), the second expert Prof. Dr.-Ing. Benno Stabernack (University of Potsdam/Fraunhofer HHI) and the third examiner Prof. Dr.-Ing. André Kaup (FAU Erlangen-Nuremberg).

Jens Brandenburg took up his work at Fraunhofer HHI in 2006 as a research associate in the Embedded Systems research group. He is now active in the Image and Video Coding group.

20th March 2018

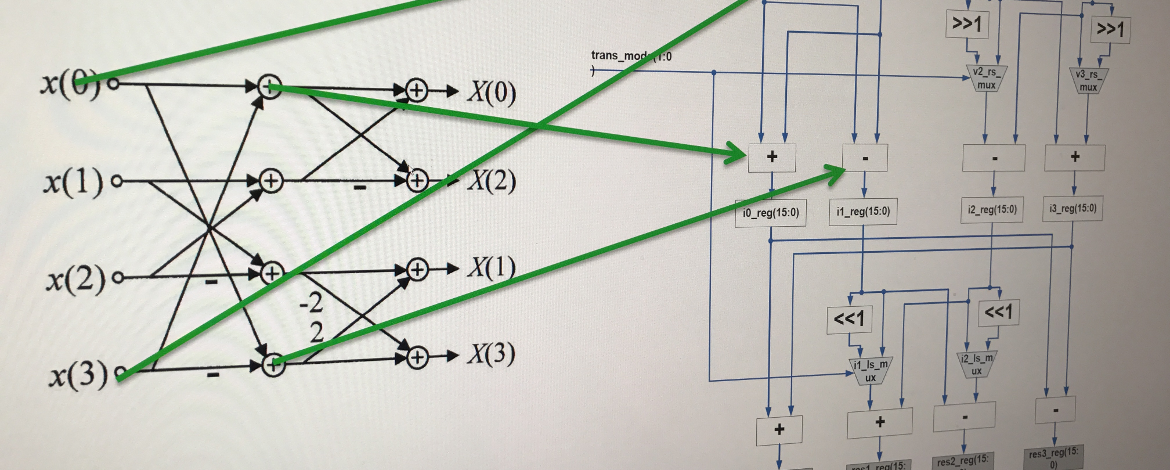

Project start research project "Next Generation Video Coding"

Dec. 1st 2017 the project "Next Generation Video Coding" started at the department.

With the increase in coding efficiency of the latest video coding methods, there is also a drastic increase in the complexity of the algorithms used and thus also in the required computational requirements.

The project is dedicated to the analysis, optimization and design of video coding techniques with a focus on cost-effective hardware implementations.

Within the next days, we will publish an official job offer for a research position in this project.

Dec. 1st, 2017