## Chipentwurf Übungsblatt 1

## 3. November 2017

- 1. Entwerfen Sie folgende Gatter in CMOS: NOT(a), NAND(a,b), OR(a,b,c), XOR(a,b), OR(AND(a,b),NOT(c)).

- 2. Gegeben seien die Funktionen  $f(x, y, z) = xy \vee x\overline{z} \vee \overline{y}z, \ g(a, b, c) = a \oplus (bc)$

- a) Bestimmen Sie die vollständige disjunktive Normalform.

- b) Bestimmen Sie den Min- und Maxterm der Funktionen.

- c) Erstellen Sie für die Funktionen das jeweilige Karnaugh-Diagramm und tragen Sie die Cubes ein.

- 3. Gegeben sei folgendes Karnaugh-Diagramm. Bestimmen Sie alle Cubes und damit die entsprechende Funktion.

|   | Α              | Ā              | Ā | Α |   |

|---|----------------|----------------|---|---|---|

| В | 1              | 1              | 1 | 1 | D |

| B | 0              | 0              | 0 | 1 | D |

| B | 1              | 0              | 0 | 0 | D |

| В | 1              | 0              | 0 | 1 | D |

|   | $\overline{c}$ | $\overline{C}$ | С | С | _ |

- 4. Gegeben sei die Funktionen  $f(x_1, x_2, x_3) = \overline{x_1} x_2 \overline{x_3} \vee x_1 \overline{x_2 x_3} \vee \overline{x_1} x_2 x_3 \vee x_1 \overline{x_2} x_3 \vee x_1$

- a) Erstellen Sie für die Funktion das Karnaugh-Diagramm.

- b) Minimieren Sie die Funktion.

- 5. Worin liegt der Unterschied zwischen kombinatorischer und sequentieller Logik?

- 6. Was ist der Unterschied zwischen einem Latch und einem Flip-Flop?

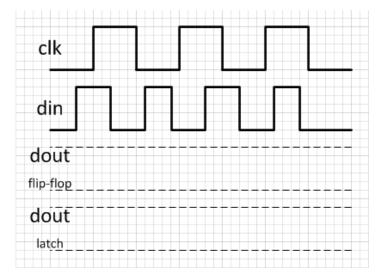

- 7. Gegeben sei folgender Signalverlauf. Zeichnen Sie die resultierenden Signalverläufe für ein Flip-Flop bzw. für ein Latch ein.

- 8. Geben Sie die logische Funktion eines RS-Latches an.

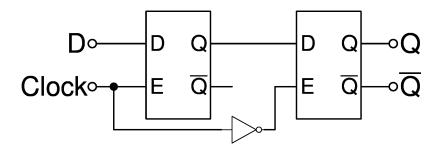

- 9. Gegeben sei folgende Schaltung Um was für eine Schaltung handelt es sich? Beschreiben

Sie die Funktionsweise anhand eines Signalverlaufsdiagramms.

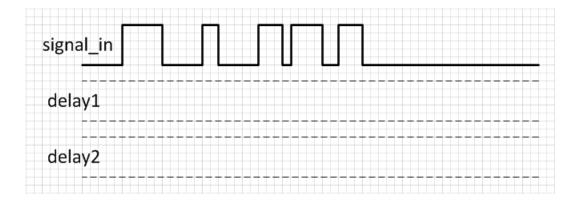

10. Welche Verzögerungsmodelle gibt es? Worin besteht der Unterschied? Zeichnen Sie die beiden Modelle in die Grafik ein. Gehen Sie dabei von einem Delay von jeweils 4 ns aus, wobei die Gitternetzbreite 1 ns darstellt.

- 11. Starten Sie die Xilinx ISE und legen Sie ein Projekt mit dem Namen ihrer Wahl an. Folgen Sie dem Wizard und geben Sie folgende Daten ein:

- 1 Tab: Projektname etc.

- 2 Tab: Family: Virtex 5, Device: XC5VLX330, Package: FF1760, Speed: -1, Simulator: ISE Simulator

- 3 Tab: New Source... → Wählen Sie "VHDL Module" und geben Sie den Namen "FA" ein. Sie können optional auf den folgenden Seiten des "New Source"-Wizards bereits die Ports der generierten Entity definieren.

- Schließen Sie die Erstellung des Projektes ab.

- 12. Implementieren Sie einen Volladdierer.

- 13. Realisieren Sie einen 16-bit Addierer unter Verwendung des Volladdierers über eine strukturelle Beschreibung.

- 14. Was sind Generics in VHDL? Erweitern Sie den Addierer, so dass die Bitbreite generisch angepasst werden kann. Definieren Sie auch einen Standardwert.

- 15. Erweitern Sie den Addierer nun so, dass das Ergebnis in einem Register gespeichert wird.

```

process (<clk>,<reset>)

begin

if (<reset> = <reset_active_value>) then

-- reset the sequential elements

elsif (<clk>'event and <clk> = '1') then

-- change the elements of the sequential elements

end if;

end process;

```